High-level Synthesis

Digital Logic Synthesis High-Level-Synthesis of digital circuits performs the transformation from an algorithmic programming language to hardware behaviour level, finally synthesized to gate-level. Target technologies are either Field-Programmable-Gate-Arrays (FPGA) used for rapid prototyping or custom designed Application-Specific-Integrated-Circuits (ASIC).

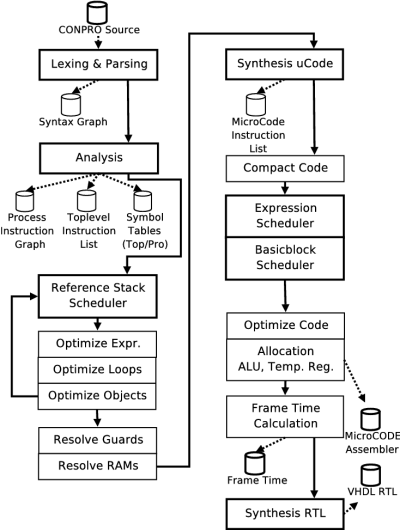

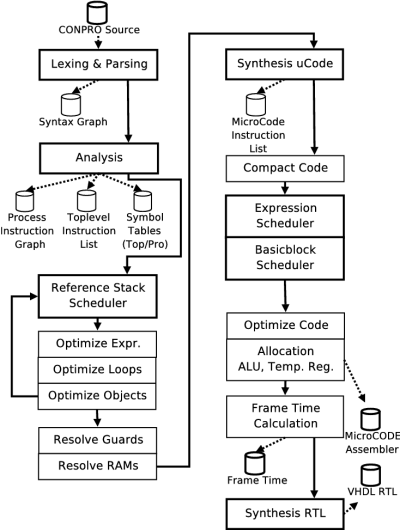

The ConPro programming language is a new enhanced imperative programming language and maps the programming level to Register-Transfer-Logic using a higher-level-synthesis approach performed by the synthesis tool ConPro, shown in Figure 1. In contrast to other approaches using modified existing software languages like C/System-C, this language is designed from scratch providing a consistent model for both hardware design and software programming. The programming model and the language provide parallelism on control path level using a multi-process model with an enhanced concurrent communicating sequential processes (CCSP) architecture, and on data path level using bounded program blocks.

Each process is mapped on a Finite-State-Machine and is executed concurrently. Process instructions are executed in the order they appear on programming level. Additionally, program blocks can be parameterized and can control the synthesis process (scheduling and allocation). Synthesis is based on a non-iterative, multi-level and constraint selective rule-set based approach, rather than on a traditional constrained iterative scheduling and allocation approach.

Required interprocess communication and synchronization is provided by a set of primitives, entirely mapped to hardware, already established in concurrent software programming (multi-threading), implemented with an abstract data type object model and method-based access.

Using the ConPro programming environment and synthesis framework it is possible to develop complex System-On-Chip (SoC) designs beyond the one million gate boundary. In contrast to traditional SoC design approaches with structural composition methods, the ConPro approach provides a behavioural and functional composition of the SoC. This synthesis approach is efficient and stable enough to create complex circuits reaching the million gates boundary.

Figure 1: High-Level-Synthesis of digital circuits from an imperative programming language using the ConPro compiler.

Interdisciplinary Science & Education Laboratory

Interdisciplinary Science & Education Laboratory

Interdisciplinary Science & Education Laboratory

Interdisciplinary Science & Education Laboratory